Product Summary

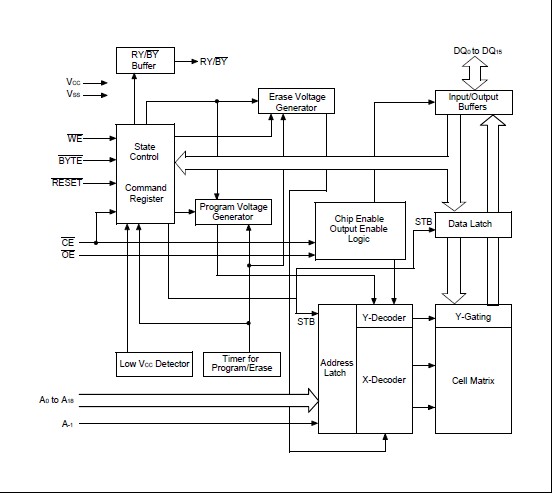

The 29F800BA-70PFTN is an 8M bit, 5.0 V only Flash memory organized as 1M bytes of 8 bits each or 512K words of 16 bits each. The 29F800BA-70PFTN is offered in a 48 pin TSOP(I) and 44 pin SOP packages. This device is designed to be programmed in system with the standard system 5.0 V VCC supply. 12.0 V VPP is not required for write or erase operations. The devices can also be reprogrammed in standard EPROM programmers. The 29F800BA-70PFTN offers access times 55 ns and 90 ns, allowing operation of high speed microprocessors without wait states. To eliminate bus contention the device has separate chip enable (CE), write enable (WE), and output enable (OE) controls. The 29F800BA-70PFTN is pin and command set compatible with JEDEC standard E2PROMs. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input; (10)to an internal state-machine which controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the device is similar to reading from12.0 V Flash or EPROM devices.

Parametrics

29F800BA-70PFTN absolute maximum ratings: (1)Storage Temperature: -55℃ to +125℃; (2)Ambient Temperature with Power Applied: -40℃ to +85℃; (3)Voltage with respect to Ground All pins except A9, OE, and RESET (Note 1): -2.0 V to +7.0 V; (4)VCC (Note 1): -2.0 V to +7.0 V; (5)A9, OE, and RESET (Note 2): -2.0 V to +13.5 V.

Features

29F800BA-70PFTN features: (1) Data Polling and Toggle Bit feature for detection of program or erase cycle completion; (2) Ready/Busy output (RY/BY) Hardware method for detection of program or erase cycle completion; (3) Low Vcc write inhibit ≦3.2 V; (4) Erase Suspend/Resume Suspends the erase operation to allow a read data in another sector within the same device; (5) Hardware RESET pin Resets internal state machine to the read mode; (6) Sector protection Hardware method disables any combination of sectors from write or erase operations; (7) Temporary sector unprotection Temporary sector unprotection via the RESET pin.

Diagrams

(Hong Kong)

(Hong Kong)